Circuits seqüencials

Els circuits seqüencials són circuits electrònics que, a diferència dels circuits combinacionals, emmagatzemen informació i operen en funció de l’estat intern del circuit, i també de les entrades de senyal. Això significa que la sortida del circuit no depèn només de les entrades actuals, sinó també de l’estat intern del circuit.

Els circuits seqüencials són blocs formats per portes lògiques bàsiques que tenen diferents entrades i sortides, i en els quals els valors dels senyals de sortida no depenen solament dels valors dels senyals d’entrada, sinó també dels valors que les mateixes sortides tenien abans.

Aquests es poden dividir en dos tipus principals: els circuits seqüencials síncrons i els circuits seqüencials asíncrons. Els circuits seqüencials síncrons són dissenyats per funcionar en sincronia amb un senyal de rellotge, que determina quan les dades són llegides o escrites en el circuit. Els circuits seqüencials asíncrons, d’altra banda, no es basen en un senyal de rellotge i són més complicats de dissenyar.

El disseny de circuits seqüencials implica la utilització de diferents elements lògics, com ara flip-flops, registres, portes lògiques i altres components electrònics.

-

- Un semàfor és un exemple típic de sistema seqüencial.

Fixem-nos en el funcionament d’un semàfor qualsevol del nostre municipi. Un semàfor és un sistema digital típic i les seves sortides són les següents:

- llum vermell per a vehicles

- llum taronja per a vehicles

- llum verd per a vehicles

- llum vermell per a vianants

- llum verd per a vianants

Aquestes cinc sortides només poden prendre dos valors diferents: llum encès o llum apagat. Com a única entrada possible, un semàfor pot presentar el polsador perquè els vianants puguin dir al semàfor que volen creuar el carrer.

Imaginem-nos que arribem a un semàfor passejant. Volem creuar el carrer però el llum dels vianants està en vermell i els vehicles circulen perquè tenen el llum verd encès. Com que tenim pressa, premem el polsador del semàfor i, després de pocs segons, el semàfor dels vehicles es posa en vermell (passant primer pel taronja) i el semàfor dels vianants es posa en verd. Fins aquí tot molt bé: quin semàfor més amable! Ens ha obeït de seguida.

Però què passarà si ara, amb el llum verd per als vianants encès, tornem a prémer el polsador? Doncs que el semàfor no ens farà ni cas i, transcorreguts uns quants segons, continuarà amb la seva seqüència de funcionament normal, deixant passar els vehicles i encenent el llum vermell per als vianants. Si pogués parlar, el semàfor ens diria alguna cosa semblant a: “No cal que tornis a prémer el polsador que ja t’he entès a la primera! Això sí: espavila’t perquè en pocs segons jo continuaré fent la meva feina i no et deixaré passar!”.

Això significa que el semàfor no sempre dona les mateixes sortides per a una mateixa combinació de les entrades. Aquest semàfor és un exemple típic de sistema digital seqüencial.

En un sistema digital seqüencial, els valors dels senyals de sortida no depenen solament dels valors dels senyals d’entrada, sinó també dels valors que les mateixes sortides tenien abans.

Cronòmetre

Penseu en un cronòmetre digital amb un polsador d’inici/aturada i un polsador de reinicialització o RESET per tornar a zero. És un sistema digital seqüencial? Per què?

Els circuits seqüencials elementals són els biestables. A partir de biestables es poden construir circuits seqüencials més complexos com, per exemple, els comptadors i els registres de desplaçament.

Us podeu trobar amb llibres tècnics que anomenen al nivell alt i al nivell baix estat de SET i estat de RESET, respectivament.

Biestables: latches i flip-flops

Un biestable és un circuit digital seqüencial que pot tenir dos estats estables a la sortida denominats nivell alt i nivell baix, en els quals es pot mantenir indefinidament.

Un biestable canvia l’estat de la seva sortida segons les seves entrades i l’estat previ de la sortida.

Els dispositius biestables es divideixen en dues categories:

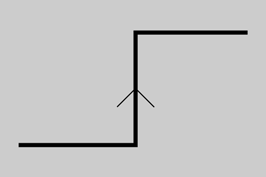

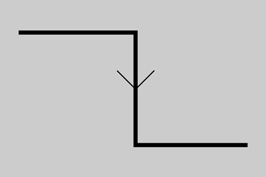

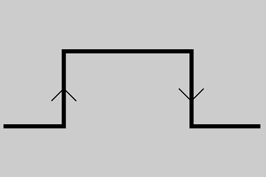

Un flanc...

… és una transició d’un senyal digital de 0 a 1 o d’1 a 0. Si la transició és de 0 a 1 s’anomena flanc positiu o flanc de pujada. Si la transició és d’1 a 0 s’anomena flanc negatiu o flanc de baixada.

- Latches: són biestables asíncrons. Això vol dir que no utilitzen cap senyal de sincronització o rellotge.

- Flip-flops: són biestables síncrons. Això vol dir que la seva sortida canvia d’estat únicament en un instant específic d’una entrada de sincronització denominada rellotge (habitualment, en un instant concret anomenat flanc).

-

- Flanc positiu

-

- Flanc negatiu

Els flip-flops es poden classificar segon el tipus de senyal de rellotge que utilitzen:

- Flip-flop disparat per flanc positiu: la sortida del flip-flop canvia quan el senyal de rellotge fa una transició de 0 a 1.

- Flip-flop disparat per flanc negatiu: la sortida del flip-flop canvia quan el senyal de rellotge fa una transició d’1 a 0.

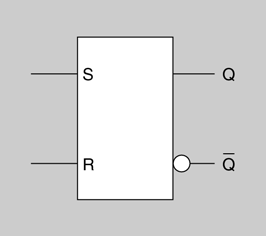

Latch S-R (SET-RESET)

El funcionament del latch S-R és el següent:

- Si posem l’entrada S (SET) a 1 i deixem l’entrada R (RESET) a 0, la sortida

del latch S-R es posa a 1: és el que s’anomena estat de SET.

del latch S-R es posa a 1: és el que s’anomena estat de SET. - Si posem l’entrada R (RESET) a 1 i deixem l’entrada S (SET) a 0, la sortida

del latch S-R es posa a 0: és el que s’anomena estat de RESET.

del latch S-R es posa a 0: és el que s’anomena estat de RESET. - Si posem les dues entrades S i R a 0, les sortides no canvien: conserven l’estat. Això vol dir posar el mateix valor que tenien abans de canviar l’estat de les entrades. Aquesta característica és molt important, perquè el latch “memoritza” el seu estat anterior.

- La sortida

sempre té el valor contrari a la sortida

sempre té el valor contrari a la sortida  (d’això se’n diu que les dues sortides són complementàries).

(d’això se’n diu que les dues sortides són complementàries).

La taula de veritat del latch S-R es mostra en la taula.

-

- Símbol lògic del latch S-R

| Entrades | Sortides | Comentaris | ||

|---|---|---|---|---|

| S | R |  |  | |

| 0 | 0 |  |  | Les sortides no canvien. Es queden en l’estat anterior |

| 1 | 0 | 1 | 0 | Estat de SET |

| 0 | 1 | 0 | 1 | Estat de RESET |

| 1 | 1 | ? | ? | Condició no vàlida |

I què passa quan posem les dues entrades del latch S-R a 1? Doncs que, a causa del funcionament intern del latch S-R, no podem predir quines sortides obtindrem.

No hem de posar mai les dues entrades del latch S-R a 1 simultàniament perquè no podem predir quin valor tindran les seves sortides. Aquesta imprecisió del valor de les sortides podria provocar problemes greus al circuit on estigués connectat el latch S-R.

En la figura podem veure l’evolució amb el temps de les les formes d’ona de les entrades i la sortida d’unlatch S-R. Se suposa que Q es troba inicialment a nivell baix. Observeu que en cap moment les dues entrades es troben a nivell alt simultàniament.

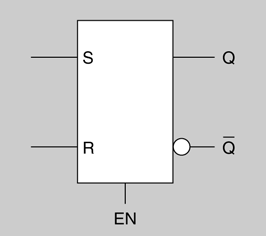

Latch S-R amb entrada d'habilitació

A un latch S-R se li pot afegir una nova entrada: l’entrada d’habilitació EN.

El nom EN d’una entrada d’habilitació ve de la paraula anglesa enable, que vol dir habilitació.

-

- Símbol lògic del latch S-R amb entrada d'habilitació

La funció d’aquesta entrada EN és molt senzilla:

- Quan l’entrada EN està a nivell alt, el latch està habilitat i funciona com un latch S-R normal.

- Quan l’entrada EN està a nivell baix, simplement el latch S-R no fa res: per molt que canviem el valor de les entrades S i R, les sortides conserven l’estat anterior.

La taula de veritat d’aquest latchS-R amb entrada d’habilitació es mostra en la taula.

| Entrades | Sortides | Comentaris | |||

|---|---|---|---|---|---|

| EN | S | R |  |  | |

| 1 | 0 | 0 |  |  | Les sortides no canvien. Es queden en l’estat anterior |

| 1 | 1 | 0 | 1 | 0 | Estat de SET |

| 1 | 0 | 1 | 0 | 1 | Estat de RESET |

| 1 | 1 | 1 | ? | ? | Condició no vàlida |

| 0 | X | X |  |  | Latch no habilitat. Les sortides no canvien |

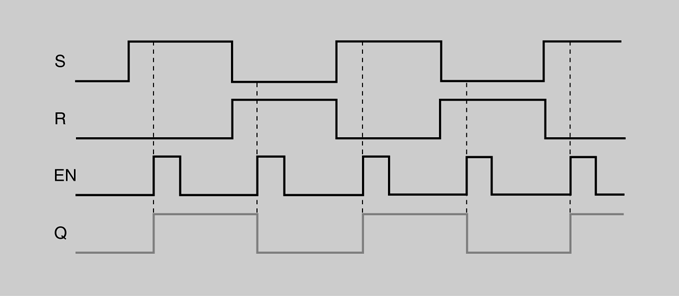

En la figura podem veure les formes d’ona de les entrades i la sortida d’un latch S-R amb habilitació. Se suposa que Q es troba inicialment a nivell baix.

Als annexos del web hi teniu disponible una simulació d’un latch S-R amb habilitació.

Flip-flop S-R

En la taula es mostra la taula de veritat d’un flip-flop S-R disparat per flanc positiu. Com es pot veure, el seu funcionament és similar al del latch S-R. L’única diferència és que les sortides només canvien en l’instant en què el senyal CLK passa de nivell baix a nivell alt.

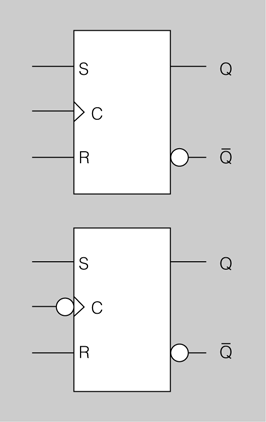

-

- Flip-flops S-R disparats per flanc positiu (superior) i per flanc negatiu (inferior)

| Entrades | Sortides | Comentaris | |||

|---|---|---|---|---|---|

| CLK | S | R |  |  | |

| X | X | X |  |  | No hi ha flanc de CLK: les sortides no canvien |

| 0 | 0 |  |  | Les sortides no canvien |

| 1 | 0 | 1 | 0 | Estat de SET |

| 0 | 1 | 0 | 1 | Estat de RESET |

| 1 | 1 | ? | ? | Condició no vàlida |

Com en el cas del latch S-R, mai no hem de posar les entrades S i R del flip-flop S-R simultàniament a nivell alt, perquè no podem predir quin valor tindran les seves sortides. Aquesta imprecisió del valor de les sortides podria provocar problemes greus al circuit on estigués connectat el flip-flop S-R.

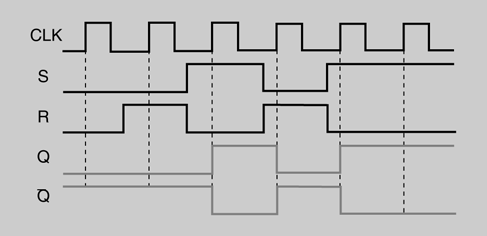

En la figura podem veure les formes d’ona de les entrades i la sortida d’un flip-flop S-R disparat per flanc positiu. Se suposa que Q es troba inicialment a nivell baix.

Als annexos del web hi teniu disponible una simulació d’un flip-flop S-R disparat per flanc positiu.

Flip-flop J-K

El flip-flop J-K és un dels tipus de flip-flop més utilitzats.

Les denominacions J i K...

… per a les entrades del flip-flop J-K no tenen cap significat conegut, excepte el fet que són dues lletres consecutives de l’alfabet.

El seu funcionament és idèntic al del flip-flop S-R en els estats d’operació SET, RESET i no-canvi. La diferència resideix en el fet que el flip-flop J-K no té condicions no vàlides com passa amb el flip-flop S-R (ara sí hi pot haver dos uns a les entrades).

El flip-flop J-K pot tenir qualsevol combinació d’uns i zeros a les seves entrades.

| Entrades | Sortides | Comentaris | |||

|---|---|---|---|---|---|

| CLK | J | K |  |  | |

| X | X | X |  |  | No hi ha flanc de CLK: les sortides no canvien |

| 0 | 0 |  |  | Les sortides no canvien. |

| 1 | 0 | 1 | 0 | Estat de SET |

| 0 | 1 | 0 | 1 | Estat de RESET |

| 1 | 1 |  |  | Basculació: la sortida canvia al seu estat oposat |

-

- Flip-flops J-K disparats per flanc positiu (superior) i per flanc negatiu (inferior)

Com podem observar en la taula de veritat del flip-flop J-K (taula), ara ja no hi ha combinacions no vàlides de les entrades, com passava al flip-flop S-R. Quan les dues entrades J i K es posen a nivell alt, la sortida canvia al seu estat oposat. És a dir, ens podem trobar amb dues d’aquestes situacions:

- Si la sortida estava a nivell alt abans del flanc de rellotge, passarà a nivell baix.

- Si la sortida estava a nivell baix abans del flanc de rellotge, passarà a nivell alt.

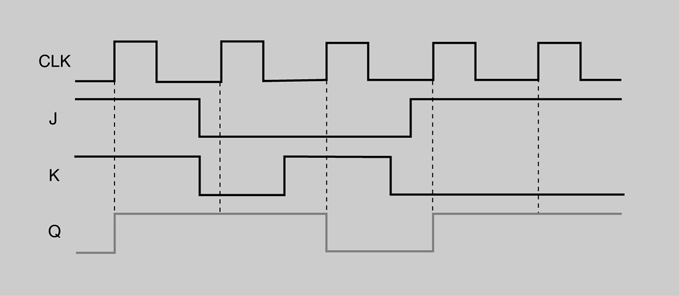

En la figura podem veure les formes d’ona de les entrades i la sortida d’un flip-flop J-K disparat per flanc positiu. Se suposa que Q es troba inicialment a nivell baix.

Circuit integrat 74HC112

El circuit integrat comercial 74HC112 és un petit xip de setze pius que conté dos flip-flops J-K disparats per flanc descendent.

Flip-flops D i T

El flip-flop D està construït a partir d’un flip-flop J-K al qual s’han unit les seves entrades J i K mitjançant un inversor, tal com es mostra en la figura. La taula de veritat d’aquest flip-flop D és molt senzilla (taula).

Als annexos del web hi teniu disponible una simulació d’un flip-flop J-K i d’un doble flip-flop J-K.

-

- Flip-flop D disparat per flanc positiu (superior) i per flanc negatiu (inferior)

| Entrades | Sortides | |||

|---|---|---|---|---|

| D | CLK |  |  | Comentaris |

| 0 |  | 0 | 1 | Estat de RESET |

| 1 |  | 1 | 0 | Estat de SET |

Com veiem en la taula, la sortida Q conserva el valor que té l’entrada D just en l’instant en el qual es produeix la transició positiva del rellotge. Aquesta propietat fa que el flip-flop D s’utilitzi molt com a element de memòria.

Als annexos del web hi teniu disponible una simulació d’un flip-flop D i d’un flip-flop D mitjançant S-R.

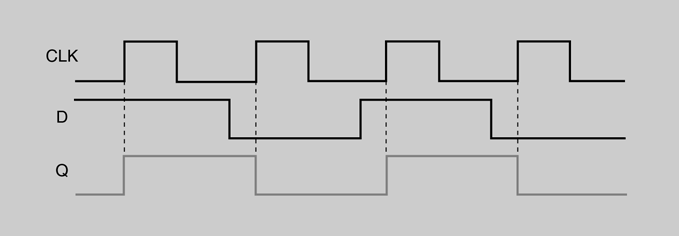

En la figura podem veure les formes d’ona de les entrades i la sortida d’un flip-flop D disparat per flanc positiu. Se suposa que Q es troba inicialment a nivell baix.

Flanc positiu o flanc negatiu?

Quan un flip-flop es dispara per flanc negatiu se simbolitza amb un petit cercle a l’entrada del rellotge. Si el flip-flop es dispara per flanc positiu el petit cercle no apareix en el seu símbol.

-

- Flip-flop T disparat per flanc positiu (superior) i per flanc negatiu (inferior)

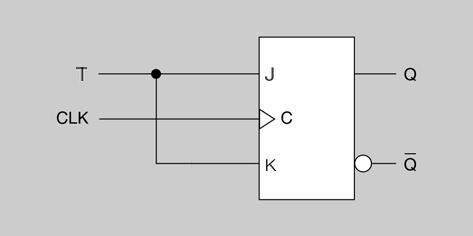

El flip-flop T està construït a partir d’un flip-flop J-K al qual s’han unit les seves entrades J i K directament, tal com es mostra en la figura. La taula de veritat d’aquest flip-flop T és molt senzilla (taula).

| Entrades | Sortides | |||

|---|---|---|---|---|

| T | CLK |  |  | Comentaris |

| 0 |  |  |  | No hi ha canvi d’estat |

| 1 |  |  |  | Canvi d’estat forçat |

Com veiem en la taula, la sortida Q canvia el valor que tenia si hi ha un 1 a l’entrada T just en l’instant en el qual es produeix la transició positiva del rellotge. Aquesta propietat fa que el flip-flop T s’utilitzi molt com a element comptador o com a complement del rellotge.

Comptadors

Un comptador (figura) és un circuit format per flip-flops T, que té una entrada d’impulsos (anomenada entrada de rellotge o CLK) i un nombre de sortides n que representen en codi binari, en cada moment, el nombre d’impulsos que li arriben a l’entrada de rellotge.

-

- Un cronòmetre és un exemple molt clar de comptador digital

La importància dels comptadors dins del món dels sistemes digitals és molt gran. Només cal pensar en el gran nombre d’aplicacions que poden tenir: detecció del nombre de vehicles que entren en un pàrking, recompte de les peces elaborades en una fàbrica, realització de funcions de cronometratge, etc.

Els comptadors digitals tenen les característiques següents:

- Mòdul: és el nombre de combinacions diferents que té un comptador a la seva sortida. Per exemple, si un comptador té 4 bits de sortida i compta des de 0000 fins a 1111, es diu que és de mòdul 16 o, de forma abreujada, és diu que és MOD16.

- Compte ascendent o descendent: gairebé tots els comptadors digitals tenen un bit d’entrada per seleccionar si el compte es fa de manera ascendent o descendent.

- Operació asíncrona o síncrona: als comptadors asíncrons, els flip-flops no comparteixen el mateix senyal de rellotge. Als comptadors síncrons, tots els seus flip-flops comparteixen el mateix senyal de rellotge. Els més utilitzats són els comptadors síncrons.

- Entrada d’esborrat: molts comptadors disposen d’un bit d’entrada que, quan es posa a zero, fa que totes les sortides es posin a nivell baix (RESET).

-

- Flancs ascendent i descendent a un pols de rellotge

- Entrada amb flanc ascendent o descendent: els comptadors amb flanc ascendent canvien la seva sortida quan en el senyal de rellotge hi ha una transició de baix a alt. Els comptadors amb flanc descendent canvien la seva sortida quan en el senyal de rellotge hi ha una transició d’alt a baix.

Els comptadors més utilitzats són els de quatre bits de sortida

Els comptadors de quatre bits de sortida poden ser:

- De mòdul 16 (MOD16): compten des de 0000b fins a 1111b (és a dir, de 0 a 15 en decimal, o de 0 a F en hexadecimal).

- De mòdul 10 (MOD10): compten des de 0000b fins a 1001b (és a dir, de 0 a 9 en decimal). Quan les sortides d’aquests comptadors estan a 1001b i hi ha un nou pols de rellotge a l’entrada, les sortides tornen a 0000b.

Per comptar nombres més grans de 16 s’utilitzen diversos comptadors de quatre bits connectats entre ells.

Els comptadors dels PLC

La majoria de comptadors que porten incorporats els autòmats programables compten fins a valors superiors a 30.000 impulsos.

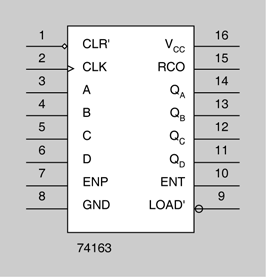

Comptador binari síncron de quatre bits 74163

-

- 74163: comptador binari síncron de 4 bits

El xip 74163 és un exemple de circuit integrat comptador binari de quatre bits.

La utilitat de cada piu d’aquest circuit comptador es descriu a continuació:

Als annexos del web hi teniu disponible una simulació d’un comptador 74163 configurat manualment i d’un comptador 74163 configurat automàticament.

- QA, QB, QC i QD (pius núms. 14, 13, 12 i 11, respectivament): sortides del comptador. QA correspon al bit de menys pes.

- CLK (piu 2): entrada de rellotge actiu per flanc ascendent.

- VCC (piu 16): alimentació del circuit integrat (+5 V).

- GND (piu 8): connexió a massa del circuit integrat.

- A, B, C i D (pius núm. 3, 4, 5 i 6, respectivament): a aquest comptador li podem indicar per quin nombre ha de començar a comptar. Normalment serà el 0000, però amb les entrades A, B, C i D li podem indicar un altra combinació d’inici (A correspon al bit de menys pes)

(piu núm. 9): quan s’aplica un nivell baix a l’entrada

(piu núm. 9): quan s’aplica un nivell baix a l’entrada  ,el comptador assumeix l’estat de les entrades A, B, C i D en el següent flanc ascendent de rellotge.

,el comptador assumeix l’estat de les entrades A, B, C i D en el següent flanc ascendent de rellotge. (piu núm. 1): entrada d’esborrat activa a nivell baix que posa a zero de manera síncrona (és a dir, en el següent flanc ascendent de rellotge) les quatre sortides del comptador.

(piu núm. 1): entrada d’esborrat activa a nivell baix que posa a zero de manera síncrona (és a dir, en el següent flanc ascendent de rellotge) les quatre sortides del comptador.- ENP i ENT (pius núm. 7 i 10, respectivament): entrades d’habilitació. Aquestes entrades han d’estar a nivell alt perquè el comptador pugui comptar. Quan almenys una de les dues entrades és a nivell baix, el comptador es desactiva.

- RCO (piu núm. 15): aquesta sortida es posa a nivell alt quan el comptador assoleix el valor 1111 a la seva sortida.

Registres de desplaçament

Els registres de desplaçament són una altra aplicació digital seqüencial que, com els comptadors, es poden obtenir mitjançant la connexió de diversos biestables o utilitzant circuits integrats específics.

Els registres de desplaçament són sistemes digitals seqüencials formats per biestables, que s’utilitzen per emmagatzemar i transferir dades digitals.

Aplicacions dels registres de desplaçament

Les principals aplicacions dels registres de desplaçament són:

- emmagatzematge de dades,

- conversió de dades paral·lel/ sèrie,

- conversió de dades sèrie/ paral·lel,

- introducció de retards en els sistemes de comunicació.

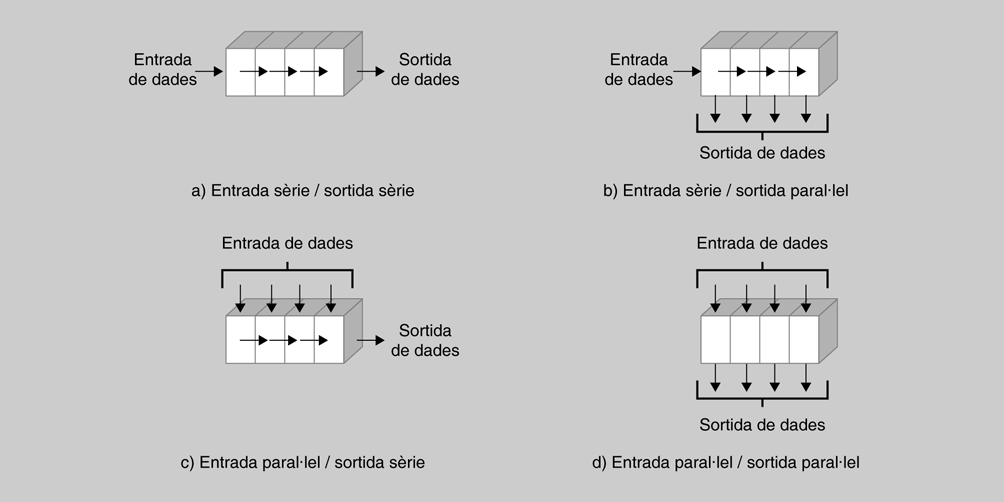

Els registres de desplaçament es poden classificar segons com s’introdueix la informació i de com s’obté aquesta informació. D’acord amb aquest criteri, podem trobar (figura):

- registres de desplaçament entrada sèrie/sortida sèrie

- registres de desplaçament entrada sèrie/sortida paral·lel

- registres de desplaçament entrada paral·lel/sortida sèrie

- registres de desplaçament entrada paral·lel/sortida paral·lel

Registre de desplaçament amb entrada sèrie/sortida sèrie

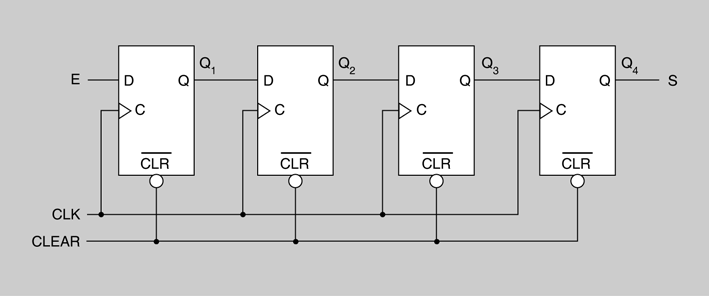

En la figura es mostra l’estructura d’un registre de desplaçament entrada sèrie/sortida sèrie de quatre bits, format per quatre flip-flops D amb senyal d’esborrat (CLR).

Estructura interna dels registres de desplaçament

La majoria dels registres de desplaçament es realitzen a partir de flip-flops tipus D.

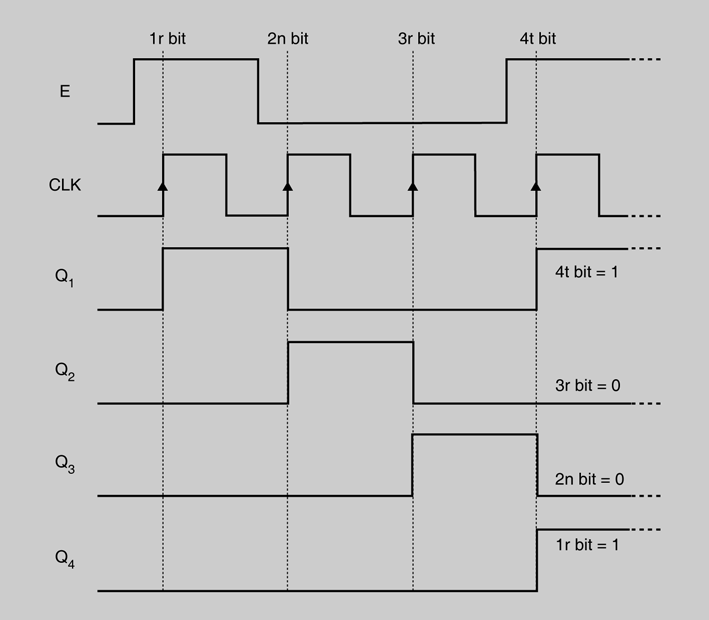

El funcionament d’aquest registre de desplaçament és ben senzill. Per l’entrada E es van introduint les dades. Cada bit dels introduïts serà desplaçat al següent flip-flop a cada flanc ascendent del senyal de rellotge, de manera que a partir del quart flanc ascendent la informació introduïda s’obtindrà a la sortida de manera successiva. En la figura es mostren els senyals E, CLK, Q1, Q2, Q3 i Q4 quan s’emmagatzema el codi 1001 en un registre de desplaçament sèrie/sèrie.

Registre de desplaçament amb entrada sèrie/sortida paral·lel

Es pot obtenir un registre de desplaçament d’entrada sèrie/sortida paral·lel partint de l’esquema del registre sèrie/sèrie. Només caldrà connectar les sortides paral·lel als punts Q1, Q2, Q3 i Q4 com es mostra en la figura. El funcionament d’aquest registre és el següent:

- Quan es produeix un flanc ascendent de CLK entra un bit per la línia E i es queda a Q1. En el mateix instant, el bit que era al punt Q1 passa a Q2, el que era a Q2 passa a Q3 i el que era a Q3 passa a Q4.

- La informació introduïda per l’entrada sèrie estarà disponible a les sortides Q1, Q2, Q3 i Q4 al flanc ascendent del quart pols de rellotge.

Registre de desplaçament universal

Un registre de desplaçament universal és un circuit integrat que incorpora els diferents modes de funcionament de registre, amb entrades i sortides sèrie i paral·lel.

MSB i LSB

MSB vol dir Most Significant Bit, és a dir, el bit més significant, el de més pes.

LSB vol dir Least Significant Bit, és a dir, el bit menys significant, el de menys pes.

-

- 74194: registre de desplaçament universal

Un exemple clar de registre de desplaçament universal és el circuit integrat 74194.

La utilitat de cada piu d’aquest registre de desplaçament universal es descriu a continuació:

(piu núm. 1): entrada asíncrona d’esborrat, activa a nivell baix.

(piu núm. 1): entrada asíncrona d’esborrat, activa a nivell baix.- S0 i S1 (pius núm. 9 i 10, respectivament): entrades de selecció del mode d’operació. Aquestes entrades actuen segons la taula.

- CLK (piu núm. 11): entrada de rellotge actiu per flanc ascendent.

- SR (piu núm. 2): entrada sèrie per fer desplaçaments a la dreta.

- SL (piu núm. 7): entrada sèrie per fer desplaçaments a l’esquerra.

- A, B, C i D (pius núm. 3, 4, 5 i 6, respectivament): entrades per fer càrregues en paral·lel.

- QA, QB, QC i QD (pius núm. 15, 14, 13 i 12, respectivament): sortides en paral·lel.

- VCC (piu 16): alimentació del circuit integrat (+5 V).

- GND (piu 8): connexió a massa del circuit integrat.

| S0 | S1 | Mode d’operació |

|---|---|---|

| 0 | 0 | Rellotge inhibit: no hi ha desplaçament |

| 0 | 1 | Desplaçament a l’esquerra |

| 1 | 0 | Desplaçament a la dreta |

| 1 | 1 | Càrrega en paral·lel de les dades a les sortides |

La càrrega en paral·lel es fa de manera síncrona, aplicant les dades a les entrades en paral·lel i posant les entrades de control de mode S0 i S1 a nivell alt. A partir d’aquest moment, les dades seran transferides a la sortida en el flanc ascendent del pols de rellotge; durant la càrrega en paral·lel, el flux de dades per l’entrada sèrie queda inhibit.

Als annexos del web hi teniu disponible una simulació d’un registre de desplaçament universal 74194.